【IT168 资讯】在前不久的FMS闪存会议上,东芝不仅展示了A19 TLC闪存(闪迪接着就出了Ultra II系列TLC硬盘),还首次公开了下一代的15nm闪存晶圆,声称这是世界上非常先进的NAND工艺,从制程上来说东芝的15nm工艺确实是非常先进的。除此之外,它的先进之处还反映在核心面积及容量密度上,仅次于三星3D堆叠技术的V-NAND闪存。

Anandtech网站日前估算了东芝15nm NAND晶圆的一些技术指标,比如核心面积、容量密度。他们使用的方法跟之前评估三星V-NAND闪存的方式一样,12英寸晶圆的面积是固定的,用PS工具计算出每个核心的长宽就可以了,详细结果如下:

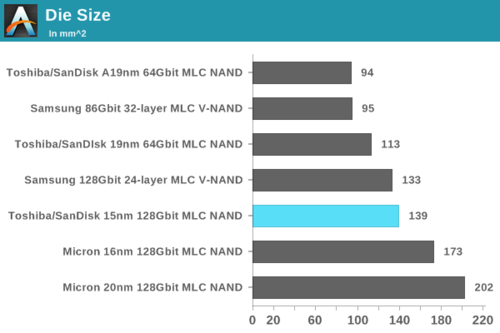

东芝128Gbit 15nm闪存的核心面积

首先是核心面积,计算出来的东芝15nm 128Gbit闪存核心面积约为139mm2,在128Gbit核心的闪存中核心面积仅比三星第一代24层堆叠的V-NAND闪存略高,大大低于美光20nm甚至16nm工艺的128Gbit闪存。

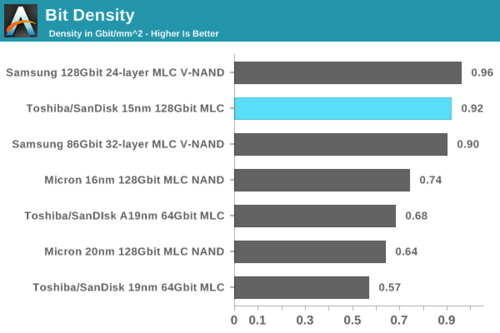

容量密度

如果计算下容量密度,那么东芝15nm 128Gbit闪存也是第二位的,容量/面积比(Gbit/mm2)仅次于三星24层VP-NAND,比之前测过的三星32层V-NAND还要高一些。东芝、闪迪联合开发的15nm闪存确实很厉害,要知道2016年他们也会进军3D堆叠闪存,届时优势还会更大。

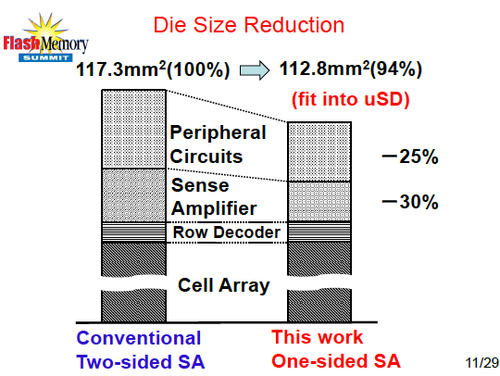

东芝15nm闪存高效的容量比源于他们使用的新技术,包括双面传感放大器(two-sided sense amp)以及ABL(all bit line)架构,有效减少了外围电路及传感放大器电路的面积,提高了闪存阵列效率。原文估计这个阵列效率(闪存Cell单元与整合核心面积的比例)在80%,这是典型的128Gbit核心的阵列效率。更高的容量往往意味着更高的闪存阵列效率,因为外部电路并不会随着制程的提升而缩小所占的面积,因此提升核心容量是降低每GB成本的关键因素之一。

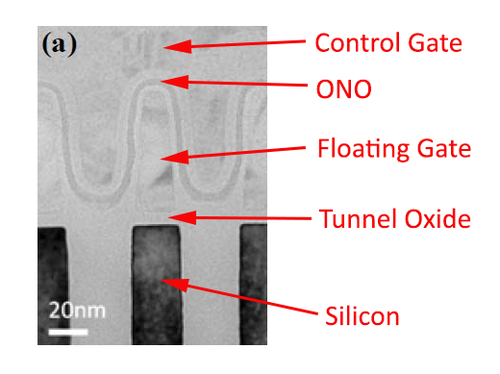

由于还没有15nm NAND核心的横截面剖图,所以现在很难确定东芝到底使用了什么方法缩小了核心面积。他们的官方说明中没有提到高K介质(High-K),因此不太可能使用High-K之类的技术。根据过往的经验,东芝、闪迪只是简单地提高了纵横比,使得浮栅极(floating gate)比其他组件更高一些,同时保持浮栅极的体积更小一些。这种设计有助于保持栅极耦合比例,因为控制栅依然覆盖在浮栅极上面,浮栅极高度提高之后,栅极之间的耦合依然有效,虽然它们的距离越来越近。

目前东芝、闪迪的15nm闪存工艺正在开始产能爬坡,基于新工艺闪存的SSD预计会在今年Q4季度出现。