【IT168 资讯】AMD对第三代推土机核心Steamroller寄予厚望,研发工程师对其性能也相当自信,豪言性能会提升45%,因为Steamroller架构是重新设计的,它才是推土机架构的本来面目。

工程师的话不能不信,也不可全信,Steamroller架构与Bulldozer推土机的设计思路还是一样的,AMD更多的是架构优化,对目前反映出的缺陷做了针对性改进,有关CPU架构改进在之前的文章中已经讲的很详细了,而Softepedia连发三文解析Steamroller架构在工艺制造上是如何优化的。

在此之前先看一点背景知识。随着CPU功能的增多,设计也越来越复杂,晶体管规模也急速攀升,推土机的晶体管规模为12亿(早先说是20亿),上一代的六核Tuban才9亿,而Intel的SNB是9.95亿,IVB则提升到14亿。

但是CPU的晶体管规模目前已经追不上GPU了,AMD的Tahiti核心有43亿个晶体管,NVIDIA的GK104也有35亿个,几乎是同代CPU晶体管规模的三倍,当然功耗和核心面积也高于CPU。

这二者的区别不仅在于工艺和架构的不同,还有一种差异则是“优化”不同。

晶圆厂一般会提供一套特殊的软件自动化工具给客户,后者可以借用这套软件来优化芯片设计,重新排列部分功能单元,由于这种工具是专门针对当前工艺设计的,因此它的效率比较高,可以大幅减少芯片的核心面积并降低功耗。

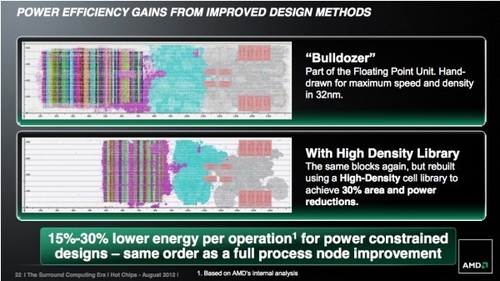

这种设计被称之为High Density cell library(高密度单元程序库),AMD在HotChips会议上讲解Steamroller架构时专门提到了使用工具优化芯片设计的重要性。

在这张对比图上,AMD演示了FPU单元使用人工及自动化工具优化设计的不同,后者可以减少30%的核心面积,功耗也会随之降低15-30%。不过自动化工具的缺点就是频率不容易提高,这也是为什么在GPU设计中它使用的更多的原因,因为GPU的频率普遍在1GHz左右,最大也就是2GHz,而主流CPU的频率大都在3GHz以上。

综合之后AMD认为自动化工具对CPU来说也是利大于弊,Steamroller的核心面积借此可减少30%,另外32nm工艺升级到28nm还会额外带来30%的核心面积及功耗降低,如此一来Steamroller处理器的功耗、核心面积都得到了平衡,甚至可与20nm工艺相媲美。

第一代推土机在GF 32nm SOI工艺下勉强达到了3.6-4.2GHz,但是代价高昂,功耗和发热比竞争对手的产品要高得多,第二代Piledriver核心重点优化了功耗和发热,旗舰型号FX-8350的频率进一步提高到4-4.2GHz,变相提高了CPU性能,不过功耗和发热还缺少实测结果。

Steamroller应用了GPU设计中的高度自动化工具来优化电路,预计功耗和发热会有明显降低,再加上新制程工艺的优势,处理器的核心面积乃至功耗甚至会有改头换面的感觉,再加上CPU架构的改进,这或许就是AMD如此自信的主要原因吧,现在我们只希望这一切都是真的。