【IT168 资讯】AMD昨天公布了下代处理器打桩机的第一张内核照片,并宣称主频会向4GHz以上迈进,那么AMD是如何做到这一点的呢?旧金山举行的国际固态电路会议上,AMD揭示了背后的秘密。

做为推土机的进化版,打桩机将会采用所谓的“谐振时钟网络”(resonant clock mesh)来提升频率,而该技术并非AMD自己的发明创造,实际上来自美国的另一家半导体公司Cyclos Semiconductor。这也是该技术认可度高次投入商用,之前只是在ARM公司的ARMv9架构上进行过理论验证。

AMD宣称,打桩机将凭此技术和其它改进将运行频率提升10%,从而突破4GHz大关,另一方面还可以在同样的频率下降低10%的功耗,且不影响热设计功耗,时钟分派功耗更是可以减少最多24%。

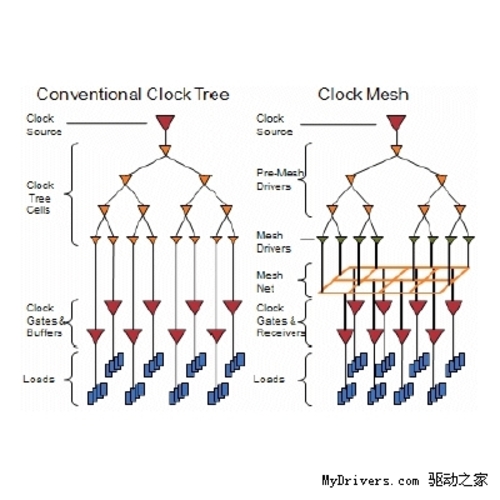

至于工作原理么,就是在时钟网络的电容器和新集成的电感器上构成谐振电路,将谐振电路的电容器和电感器之间交换能源时的电气信号作为时钟来使用。谐振时钟网络会使用片内电感器创建一个“电摆”(electric pendulum)或者叫“振荡回路”(tank circuit),利用Cyclos的电感器和时钟控制电路去重新利用时钟功耗,而不是在每个时钟周期内将它们白白排除掉。

谐振电路本身就是时钟发生源,因此无需像已有时钟网络那样使用很大的时钟缓冲器,只不过初始截短需要激发能量交换,而且当谐振电路损失导致能量交换减缓时,还要再次激发。Cyclos声称,即便是如此,这些激发所需要的功率也远远小于已有时钟网络的时钟缓存器的驱动功率。

AMD高级院士Samuel Naffziger表示:“我们已经将Cyclos IP无缝集成到了现有的时钟网络设计流程中,所以在开发进度方面没有任何风险。测试结果完全符合我们的预期,没有增加核心面积,也能利用标准的制造工艺(GlobalFoundries 32nm),所以在谐振时钟网络上的投资是完全值得的,我们的客户也需要更高效的处理设计。”

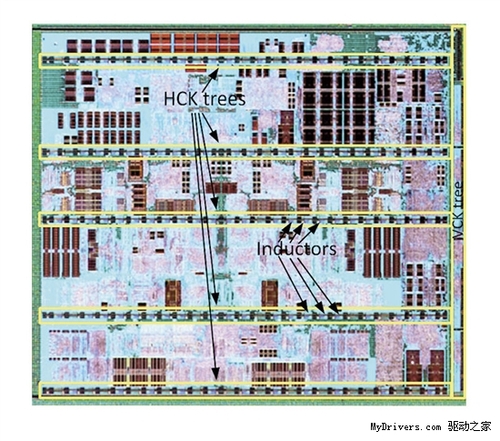

按照Cyclos给出的数据,该技术会使处理器核心面积增大约4-5%,但因为处理器设计都会保留一定的冗余空间,新增的电感器可以说是嵌入在了保留的“空地”上,因此最终保持核心面积基本不变是完全可能的。

Cyclos推算,要提供超过1GHz的时钟,需要集成0.75-1.25nH的电感器,其面积不超过100×100μm。

Cyclos方面对于自己的技术能得到AMD青睐也是激动不已,其创始人兼总裁Marios Papaefthymiou表示:“Cyclos的技术已经得到了验证,我们也期待能借助自己开发的设计自动化工具,将其推入更多SoC设计。我们相信,谐振时钟网络是实现GHz频率、超低功耗嵌入式处理器IP的关键所在。”